PowerVR Rogue USC¶

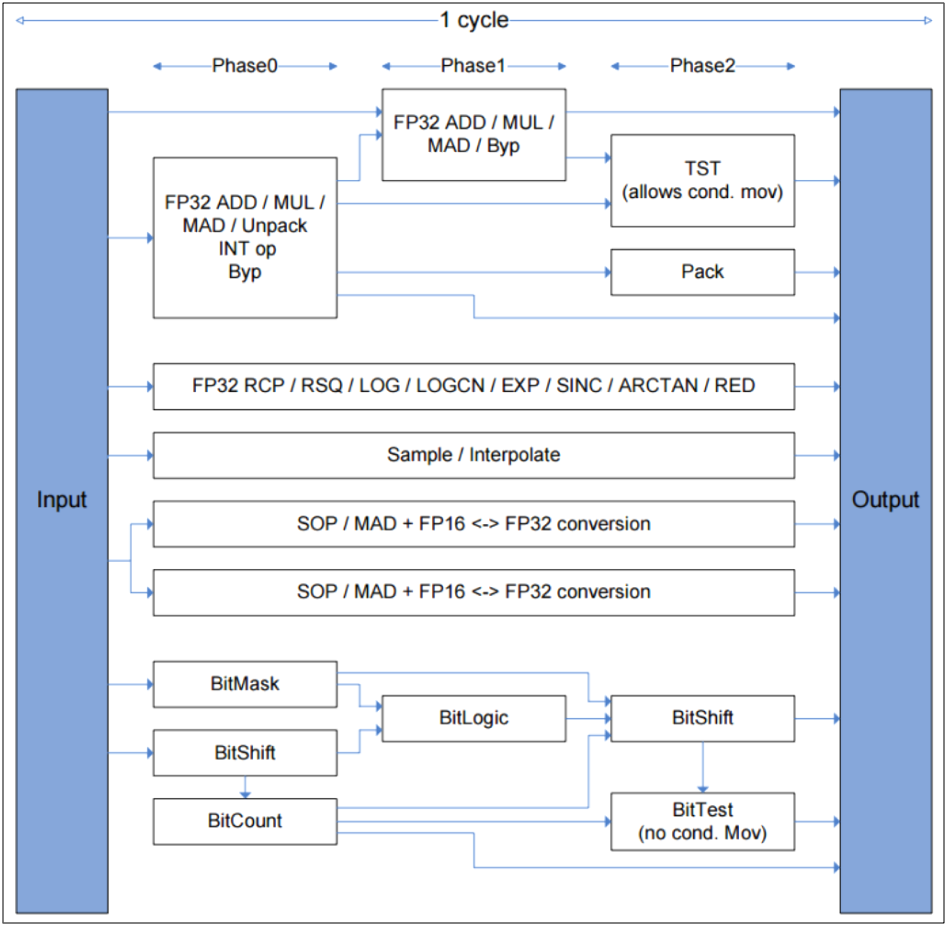

Shader performance on PowerVR Rogue architecture GPUs depends on the number of cycles it takes to execute a shader. Depending on the configuration, the PowerVR Rogue architecture delivers a variety of options for executing multiple instructions in the USC ALU pipeline within a single cycle. Some of these instructions are explained in more detail further along in this guide.

For example, it is possible to execute all of the following in one cycle:

Two F16

SOPinstructionsThe F32 <-> F16 conversions

The

MOV/OUTPUT/PACKinstruction.

As can all of these in one cycle:

An FP32

MADAn FP32/INT32

MAD/UNPACKinstructionA test (conditional) instruction

The

MOV/OUTPUT/PACKinstruction.

If there is bitwise work to be done, these can all be executed in one cycle too:

A bitwise SHIFT/COUNT

A bitwise logical operation

A bitwise SHIFT

A test (conditional) instruction

The

MOV/OUTPUT/PACKinstructions.

Other possibilities for execution in one cycle include:

A single complex operation (such as

RCP) and aMOV/OUTPUT/PACKinstructionAn interpolate/sample instruction plus the usual

MOV/OUTPUT/PACKinstruction.

As shown in the diagram below, it is best to use all stages in one route in the pipeline below to make full use of the ALU. Therefore, GLSL instructions should be arranged in that way.