Vertex Processing (Tiler)¶

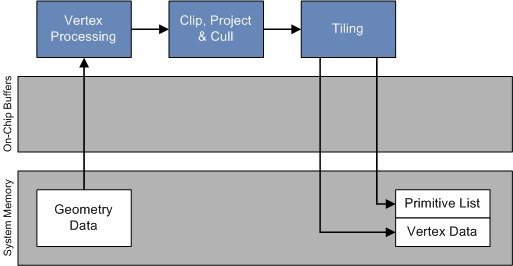

Every frame, the hardware processes the submitted geometry data with the following steps:

Application-defined transformations, such as vertex shaders (Vertex Processing), are executed.

The resulting data is converted to screen-space (Clip, Project, and Cull).

The Tile Accelerator (TA) determines which tiles contain each transformed primitive (Tiling).

Per-tile lists are updated to track the primitives that fall within the bounds of each tile.

Each tile in the tile list contains primitive lists that include pointers to the transformed vertex data. The tile list and the transformed vertex data are both stored in an intermediate store called the Parameter Buffer (PB). This store resides in system memory, and is mostly managed by the hardware. It contains all information needed to render the tiles.